Matthew Venn

@matthewvenn

Followers

12K

Following

9K

Statuses

9K

Engineer and Technology Communication. On a mission to make ASICs more accessible. YosysHQ & Tiny Tapeout founder member. @mattvenn.net on blue sky

Valencia, Spain

Joined January 2009

RT @PsychogenicTech: @MattDIYgraphics @tinytapeout @matthewvenn @UriShaked I derive an inordinate amount of satisfaction seeing anything I…

0

1

0

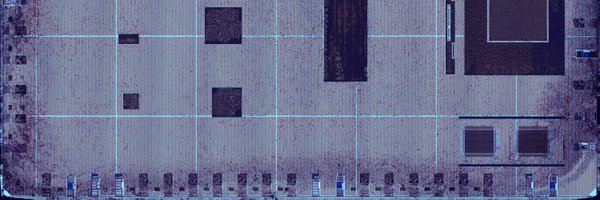

RT @MattDIYgraphics: My @tinytapeout 7 chip has arrived and it WORKS! This is a tiniest ASIC GPU. Render two polygons max. Thank you @mat…

0

19

0

RT @Hacksterio: Sylvain Munaut combines two Tiny Tapeout projects to create an open-silicon software-defined radio.

0

8

0

SPICE is the #ASIC terminology of the week! In the last month, SPICE has been the 17th most popular out of 42 terms.

0

1

7

Don't miss my next open source silicon stream! As well as the latest news and events I'll be looking at some new silicon proven designs and look at reading and writing via SPI. #opensourcesiliconstream #siliconproven #tinytapeout #asic

0

3

7

Watch me unbox @tinytapeout 7 and test my twin tee oscillator design inspired by @AlanAtTek Taken from my #opensourcesiliconstream - every Monday at 17:00 CET

1

12

85

@zeroverhe No I don't. We're basically dependent on a fab that can support those technologies opening up a PDK.

1

0

1

Simulation is the #ASIC terminology of the week! In the last month, Simulation has been the 35th most popular out of 42 terms.

0

5

18

Shuttle is the #ASIC terminology of the week! In the last month, Shuttle has been the 16th most popular out of 42 terms.

0

4

8

RT @zzznah: A big day for my circuit simulator: automatic analysis of stateful cells seems to work (sometimes)

0

7

0

RT @arturo182: Not related to anything, but did you know you can use my Starter Pack on 🦋 to instantly follow 140+ cool people in the Elect…

0

7

0

RTL is the #ASIC terminology of the week! In the last month, RTL has been the 37th most popular out of 42 terms.

0

2

5

Join me today for another #opensource #silicon #stream! I plan to look at Vincent Fusco's 555 timer on TT06 and use an SDR to see what kind of radio signals I can get out of a TT07 or TT06 #ASIC.

0

5

20